楼主 # 2024-03-25 17:57:35 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 52

- 积分: 163

AG RV2K 调试

把supra分解后获取bin单独调用

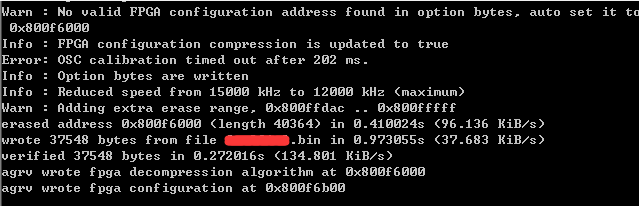

然后用脚本搭建了windows下的命令行环境,包括fitter和downloader,一键产生bit file(bin)和一键下载。fitting成功,download过程出现校准片内硅振荡器出现错误,何解?

最近编辑记录 aquasnake (2024-03-25 18:07:17)

离线

楼主 #1 2024-03-25 19:13:47 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 52

- 积分: 163

Re: AG RV2K 调试

我测试了下极限fitting利用率是89%,基本上大概是在1890个LUTs,我跑了上百次,只要综合产生的LUT超过189x,基本上fitter就跑不出来。

因此大致情况下稳定跑出来基本控制利用率在89%以下,当然我还是用的几个月前的fitter,如果是近一两个月supra下的fitter,更难跑出来,效率更降低了。因此我建议不要盲目跟随原厂升级tools,如果你以前做的稳定的项目,非必要不要升级

离线

楼主 #2 2024-03-25 20:38:59 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 52

- 积分: 163

Re: AG RV2K 调试

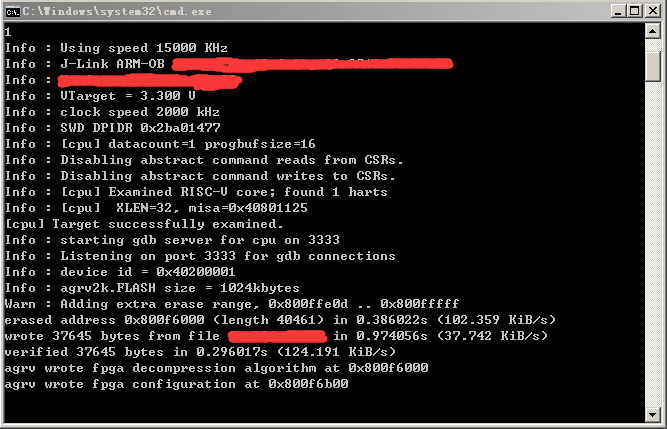

似乎已经下载成功

openocd能获取到device id,基本可以认为已经可以通过swd访问到芯片

离线

楼主 #4 2024-03-26 09:32:35 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 52

- 积分: 163

Re: AG RV2K 调试

目前我只能用到89%,一旦资源用到超过1890 LUTs,fitter就跑不出来。不清楚是不是工具限制了产生bin的size大小还是其他什么。mcu的firmware分配到内部flash是从低到高,cpld的bit bin是高空间活动分配(起始地址0x800fffff - cpld bin size),中间必然有一个分界,可能是内部flash不够多,只能限制了size,因此也限制了cpld的充分使用,不知道某些具有更多内部flash容量的rv2k是不是这种情况

最近编辑记录 aquasnake (2024-03-26 09:33:24)

离线

楼主 #5 2024-03-27 08:29:19 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 52

- 积分: 163

Re: AG RV2K 调试

目前 agm尚且还需要altera环境,来注入外挂脚本利用quartus ii产生网表,这部分无法自动化,其他我都实现了一键批处理

离线

楼主 #6 2024-03-27 10:46:14 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 52

- 积分: 163

Re: AG RV2K 调试

int OSC calibration失败的原因已经解决,对Jlink-OB下载线的vcc 3.3v供电很敏感. 偏差0.5V都不行。

我因为通常习惯在jtag调试器对target板供电为了防止反向灌流加个二极管,由此导致了vcc的压降,造成校准失败。

虽然我已经让校准通过,但是我对校准精度不报大的期望,当然,这个内部晶体时钟我只用来对信号延迟计数用,并不涉及其他,请不要学我,我任何时候都是把器件用到很抠门的地步,能省一颗料则省。

最后还是希望agm在这里对内部晶体供电做一个补偿,是否考虑内部供电统一安排到2.5v vcc(vddio除外),以便当用户在使用欠压下载线的时候能够保证内部晶体的稳定

最近编辑记录 aquasnake (2024-03-27 10:48:20)

离线

楼主 #7 2024-03-27 11:06:41 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 52

- 积分: 163

Re: AG RV2K 调试

由于calibration内部晶体用的电压和目标板stand alone工作时的电压可能有偏差,因此校准到的晶体输出频率不等于实际工作时候的频率,由此可以推断,必须保证下载线输出3.3V和板子实际工作后的VCC尽可能地保持一致

同时,猜测AGRV2K内部甚至没有LDO对这个int OSC供电,而是直接跟随系统VCC 3.3V

l

离线

楼主 #8 2024-03-29 12:19:15 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 52

- 积分: 163

Re: AG RV2K 调试

fitter效率突破不了90%上限的问题,可能是无法解决的,我试图编辑.qsf文件的约束参数也没有什么优化,基本上原厂提供的配置就已经到达极限了。 也并非的工具的问题,我发现agm用的约束参数就是quartus ii兼容的(这里面很奥妙),cyclone 4架构或许就是需要剩余一部分面积才能布局布线走出来,而阉割到2K或许无法保证剩下的10%的面积连成一片,零散的10%的面积或许就是无法利用起来的,甚至无法插入一个锁存/触发模块

基于LUT结构的FPGA,Verilog代码需要写的尽量对称,所谓对称,就是if或者case语句内尽量具有相同的表达式结构,越对称,便于合并相同逻辑,综合的效率越高。同时尽量把case的所有分支都填充满,条件越详细,反而综合后分配的LUT越少。

虽然fitter的优化约束无法扣出资源,但是在综合这个步骤,通过改写代码,统一表达式结构,同样扣掉了几十个LUT出来,以前我做IC设计bring up时候的痛苦回忆又回来了,要跑通一个优化的配置,可能需要跑上百次verification. 通常效率最高的时候是在半夜,这个时候没有人和你争服务器job现程。而在白天,比如在一间科技公司,几百号人争夺代码服务器上的cpu资源,通常很难跑的快

最近编辑记录 aquasnake (2024-03-29 23:24:11)

离线

楼主 #10 2024-04-01 10:32:18 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 52

- 积分: 163

Re: AG RV2K 调试

agm的toolchain其实是属于外挂,对quartus ii做了一定程度的注入,migration以后产生的quartus ii的工程文件,然后就是利用quartus ii综合,此时需要运行agm的外挂脚本(af_quartus.tcl),脚本中把综合的约束条件自动注入综合器(它会覆盖原始quartus ii中的综合setting优化设置),产生网表

然后执行agm的fitter(af.exe)去布局布线,此时注入fitter的约束条件,同时根据.ve的pin脚分配产生bin。

在利用quartus ii做综合的的时候,一旦运行了agm的脚本,如果再次去修改ide的全局综合优化设置,就会改变外挂之前设置好的参数,所以,一旦运行脚本(af_quartus.tcl)后,就不建议去做其他setting修改,这会导致产生一些非预期的问题,唯一能做的就是点箭头start compilation

如果你在次过程中,不慎修改了setting,那么最好还是再次运行一下外挂脚本(af_quartus.tcl)

由于是外挂,因此步骤上是必须严格按照顺序的,点错了,或者中间修改了ide设置,都有可能破坏注入参数

离线

楼主 #11 2024-04-01 10:38:16 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 52

- 积分: 163

Re: AG RV2K 调试

仅仅是引脚更改,那么其实不用在quartus ii里面做编译,只需要修改.ve文件,然后再次执行af.exe就可以了。

我直接是把fitting, downloading写成了脚本一键运行, 因为fitting有时候跑一次跑不出来,会error,要多跑一次才会顺利通过,因此一键运行加速了我开发的时间,这样我完全抛弃了supra前端

最近编辑记录 aquasnake (2024-04-01 10:58:11)

离线

楼主 #13 2024-04-03 19:27:44 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 52

- 积分: 163

Re: AG RV2K 调试

@jiaowoxiaolu

因为控制字写在 ur_project.qsf文件中,这个文件其实也是一个脚本,会被af.exe调用

然而约束控制字都是altera的东西,你甚至可以在altera的工程目录下找到类似的.qsf文件,然后把需要约束的管脚配置字,摘抄过来

为什么agm不公开这些?因为这些东西是altera/intel的,quartus ii中用户不必关心.qsf文件,直接在assignment editor中有配置,配置完毕后会自动更新.qsf。而在agm中,是直接编辑这个.qsf文件。

我一开始也尝试去向供应商询问这些东西,但是基于某些原因,没有获得我需要的解答,因此都是自己慢慢啃生肉。当然,在此过程中已经了解为什么会不解答这些技术问题。因为这涉及到agm对altera的软硬件做了什么的问题,这些问题是不方便原厂自己公开释放的

最近编辑记录 aquasnake (2024-04-03 19:28:43)

离线

楼主 #15 2024-05-10 23:29:25 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 52

- 积分: 163

Re: AG RV2K 调试

用开源的综合器裸奔,就不能用quartus ii里面MegaWizard IP的东西了,这些都是绑定到IDE的闭源IP库。除非你用你自己反向出来这些模块并以代码方式嵌入到你自己的项目

离线

楼主 #16 昨天 11:22:21 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 52

- 积分: 163

Re: AG RV2K 调试

片上振荡器是精度5%??

而且RC振荡器在上电起振有一段时间的预热时间才能稳定。 如果这个预热稳定时间,大于系统RESET时间,而且又用这个片上振荡器作为信号整形、延迟或者分频等精确用途的话,比较难以搞定。

但是系统reset时间又不能做太长,这是cpld,不是单片机,需要瞬时启动特性。我在尝试如何把这个5%精度又需要上电时间的黑科技玩起来用来代替真正的外部时钟源

最近编辑记录 aquasnake (昨天 11:32:56)

离线

楼主 #17 昨天 13:36:34 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 52

- 积分: 163

Re: AG RV2K 调试

如果用开源的综合器产生网表,那么要做的事情很多,需要手动写 *asf

先借用quartus ii跑一遍,跑之前先assignment editor配置好虚拟的管脚约束,然后点af_quartus.tcl运行产生网表,以及altera的*.qsf文件。然后跑一次fitter,会自动将altera的*.qsf迁徙到AGM的 .\alta_db\alta.aqf, .\alta_db\alta.asf

但是,这两个约束并不是最终的,最后,将ur_project.asf里面的设置再次覆盖,所有的参数都是altera quartus ii里面的,因为他这个fitter是衔接quartus ii的。

假设用第三方开源的综合器产生网表,但是这些文件并不会导出,也不会是quartus ii的参数,因此会出现丢失pin脚约束和其他全局约束的情况。fitter还是会调用 .\alta_db\alta.aqf, .\alta_db\alta.asf 去约束,而这几个都是quartus ii环境下的,它与quartus ii强耦合

最乐观的情况是你上次成功编译后管脚约束是正确的,你又会手动编辑ur_project.asf。而且你的项目对于pin脚约束(上拉,OD,驱动力,滞回,延迟微调整等)不敏感

离线

楼主 #18 昨天 13:47:28 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 52

- 积分: 163

Re: AG RV2K 调试

切记一定要用商用IDE,不要用开源的东西。开源的东西不成熟,要把开源的搭建成可以商用的程度,差不多就是搭建环境,这需要一个TEAM的人力,少说也要3个人一个月的高强度工作。

或者是,一个人单独磨半年1年,搞出一套环境,当然搞出了这套环境你也只能自己用。自己一个人做点别人搞不了,不屑于搞的东西,而且原厂又不知道。

离线