- 首页

- » 搜索

- » james_juan 发表的帖子

页次: 1

#1 Re: 全志 SOC » F1C100S当作SPI Slave使用,TX資料無法傳出 » 2024-04-01 10:46:00

后来发现问题主要是出在RFRDYIF没有发生预期的中断

我预期RFRDYIF应该要在收到每一笔资料后都要产生一次中断

但实际上并没有

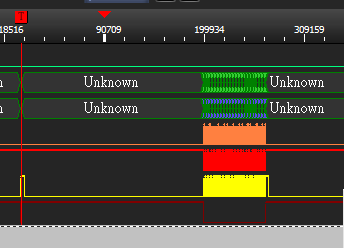

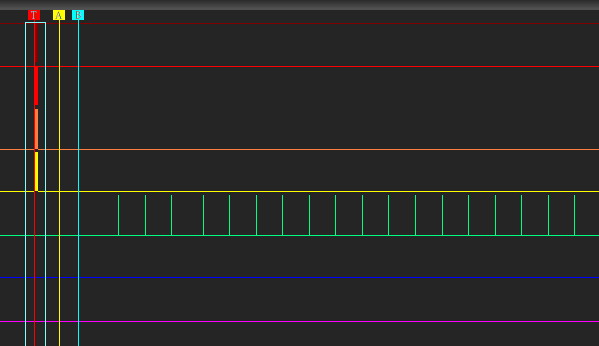

我在RFRDY的中断内加入assert IO的程式码

让他每次中断都能产生一次IO pulse

在我接上逻辑分析仪后

第一欄就是IO pulse的脚位

发现他的RFRDY并没有在SPI运作时中断

请参考下图1,在传输过程中都没有pulse

而是在SPI 传输结束后,整整delay了10ms才开始

并且每隔10ms才产生一次

请参考下图2.pulse在传输结束后才开始

改用RX DMA

SPI硬体也没办法自动传出来Rx资料

实在不知道这边硬体是如何trigger DMA

关于TxD传输资料的问题

我改用Tx DMA之后就正常了

看来是SPI硬体设计在slave mode下有问题

我目前觉得可能要一直去pull Rx FIFO counter的计数才有办法解决

若有其他先进知道相关问题的可能解法

还请各位指导

#2 全志 SOC » F1C100S当作SPI Slave使用,TX資料無法傳出 » 2024-03-26 14:08:55

- james_juan

- 回复: 1

各位好

我有个专案是Bare Metal并将F1C100S当作SPI Slave来使用

目前SPI的RXD可以接收资料

但是TXD无法将资料传送出去

TX FIFO会被直接填到满

不会在每次Master传送时pop out TX FIFO

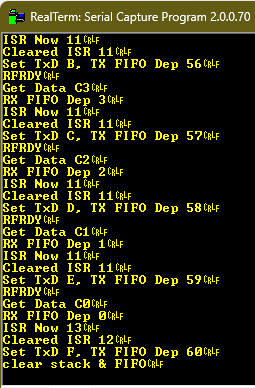

请各位参考附图的状况

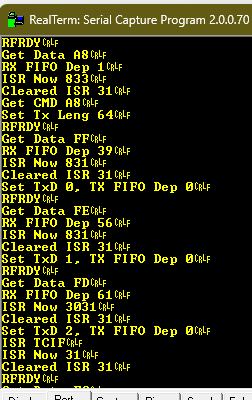

是我用UART传送出来的debug讯息

通讯设定是MASTER会传送1Byte指令 0xA8 跟64Byte dummy内容从0xFF~0xC0

F1C100S接收到0xA8后,回传64Byte资料 内容是0x00~0X0F循环

附图1显示F1C100S有正确收到0xA8并开始回传资料

但要到TxD = 2时,才有TCIF,理论上每次TXD有传送完成都要发生TCIF才对

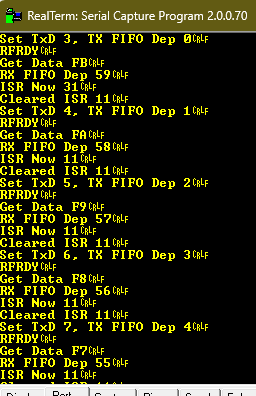

附图2 TxD = 4时,TX FIFO开始被填满

Rx FIFO的water level显示不正却,但接收中断与资料顺序是正确的

附图3 是显示最后传送64byte时的状态

TX FIFO会被填到60

但我当作MASTER测试用的Arduino只会收到0x00,

为避免可能是杜邦线断掉,我有接上逻辑分析仪来直接看F1C100S的脚位,是相同的结果

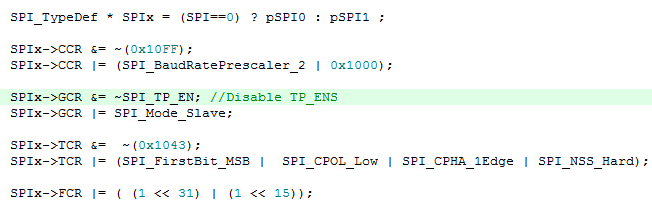

目前SPI的 FCR是使用预设值

其他设定请参考附图4

还麻烦各位先进指导一下

谢谢

页次: 1

- 首页

- » 搜索

- » james_juan 发表的帖子