楼主 #1 2021-05-22 13:27:02 分享评论

- laplace

- 会员

- 注册时间: 2021-03-05

- 已发帖子: 18

- 积分: 65

全志H3四层板制作分享,从开始学allegro 到完成第一块高速板

自己学习了allegro,一直想画一块板子,自己画原理图,自己layout,然后打板出来,最后让linux跑起来,最后学一点linux,在论坛看到了大佬们的H3,我也想尝试下。

首先我找到了H3官方资料(吴川斌那里下的),这样原理图设计就有参考了,比较快。然后就是画PCB。

配置方面:USB*2

HDMI

耳机

按键*1

1个自定义LED 学习linux点灯用,哈哈哈

1个MPU6050的陀螺仪 进一步学习linux驱动使用

DDR3 512M *2

EMMC 5.0

WIFI

TF卡

PCB采用4层板,嘉立创打板,jlc2312结构。

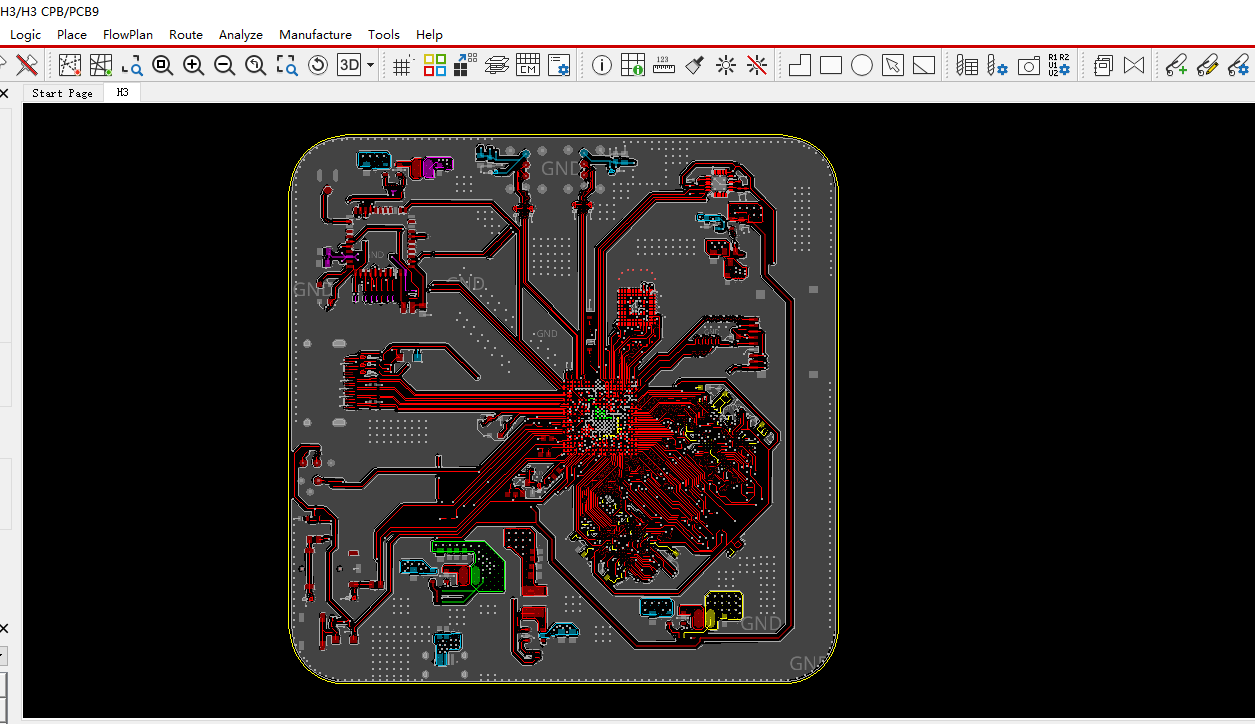

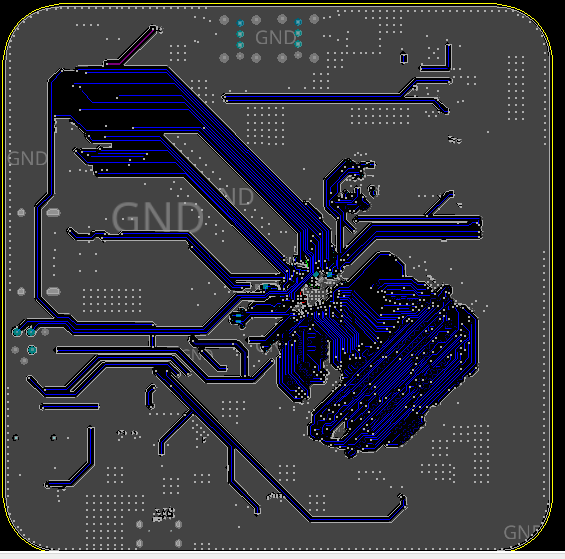

画完的板子:

TOP层

GND02层

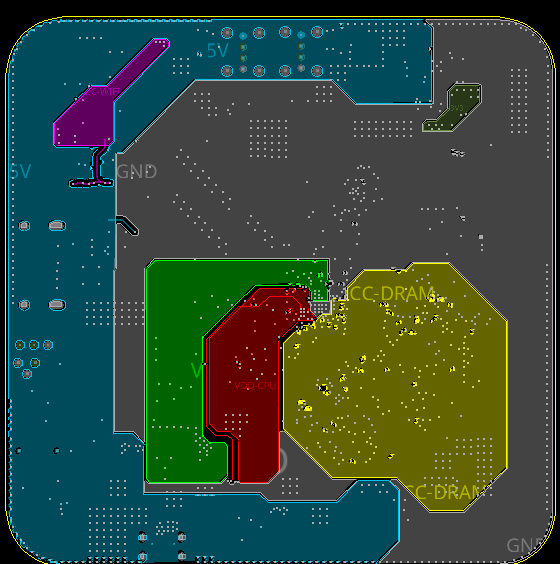

POWER03层电源分割

BOTTOM层

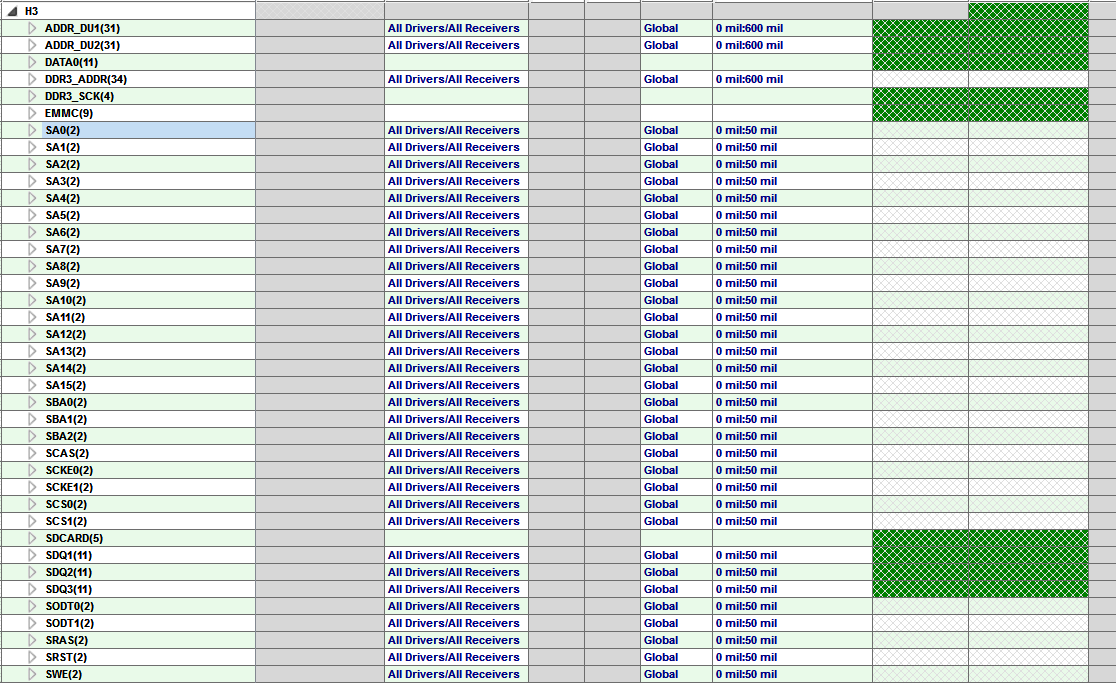

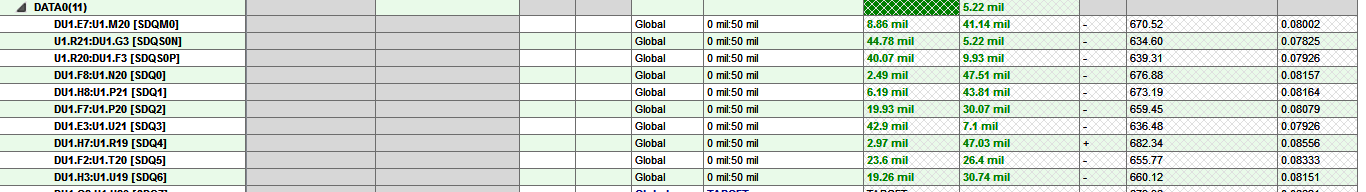

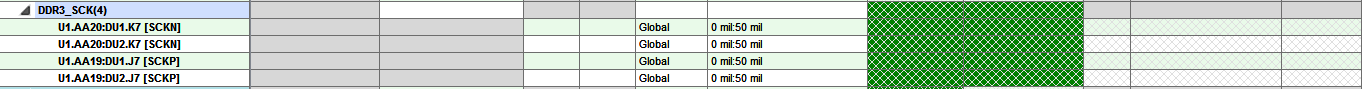

首先说说DDR3部分,T拓扑,在嘉立创打板50欧姆线宽为5.78mil,这使得布线比较紧凑,就没有满足3W原则,走的2倍线宽。

参考原厂DEMO:

不同地址线之间等长600mil,同一网络等长50mil

数据线组内等长50mil

时钟等长50mil

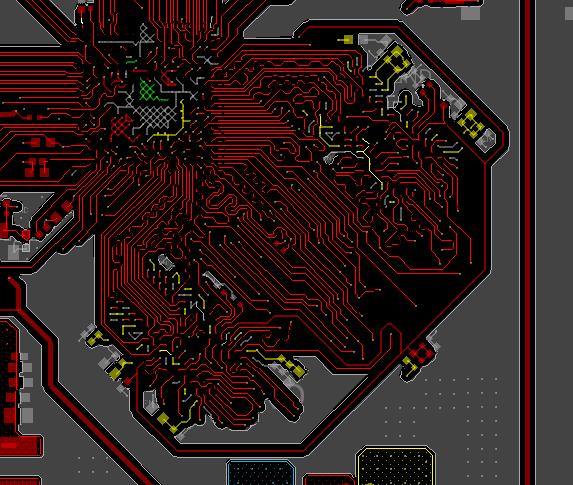

DDR3 TOP面走线:

走线比较乱,线间距比较小,主要是线宽有点大

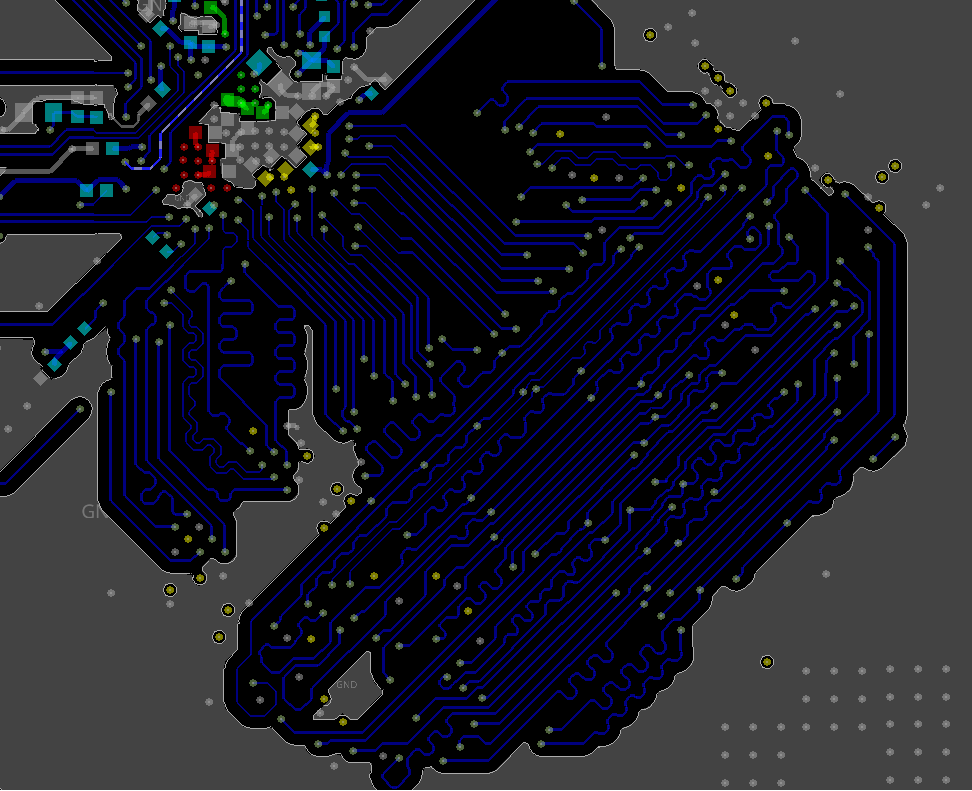

DDR3 BOTTM面走线:

为了等长也是走得一团乱

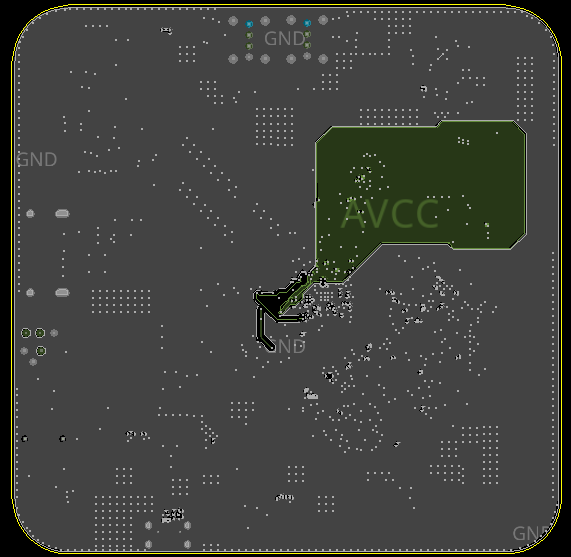

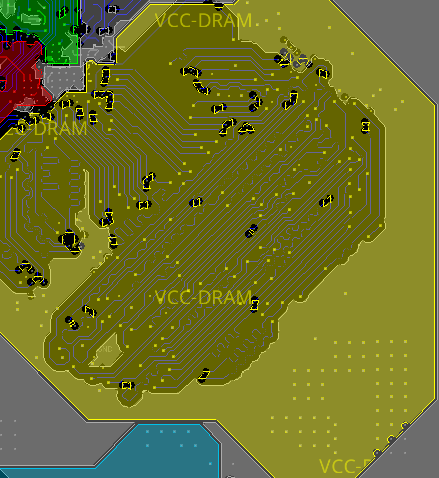

内层保证平面完整:

TOP层参考GND02层

BOTTM层参考VCC_dram:

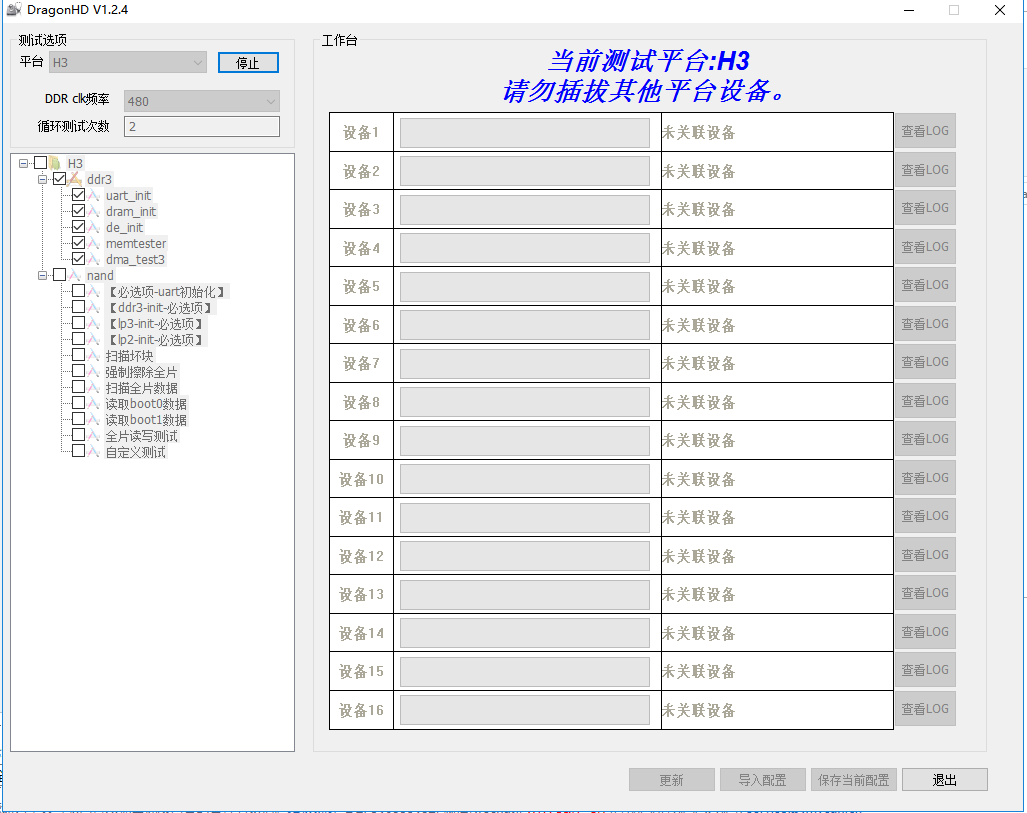

我今天使用DragonHD测试DDR3,我接的USB0,不知道为什么,没有任何反应,点了启动一直是下面这样:

恳求大佬们给我讲下这个软件怎么用的,是不是还需要什么驱动啊,我现在一头雾水。

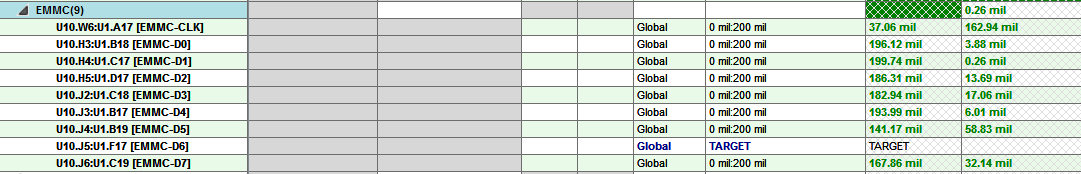

EMMC:

EMMC就做的200mil等长,现在还没使用EMMC

参考GND02层 VCC_IO_3.3V,保证平面完整。

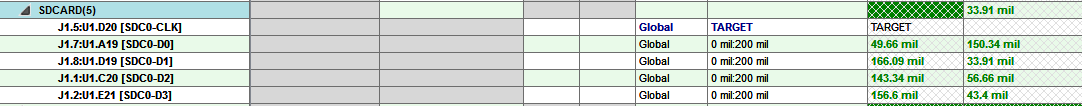

tf卡也是200mil等长:

HDMI:

hdmi原厂要求不走蛇形线,等长要求宽松,直线拉通就是了,比较简单。

USB 对内5mil

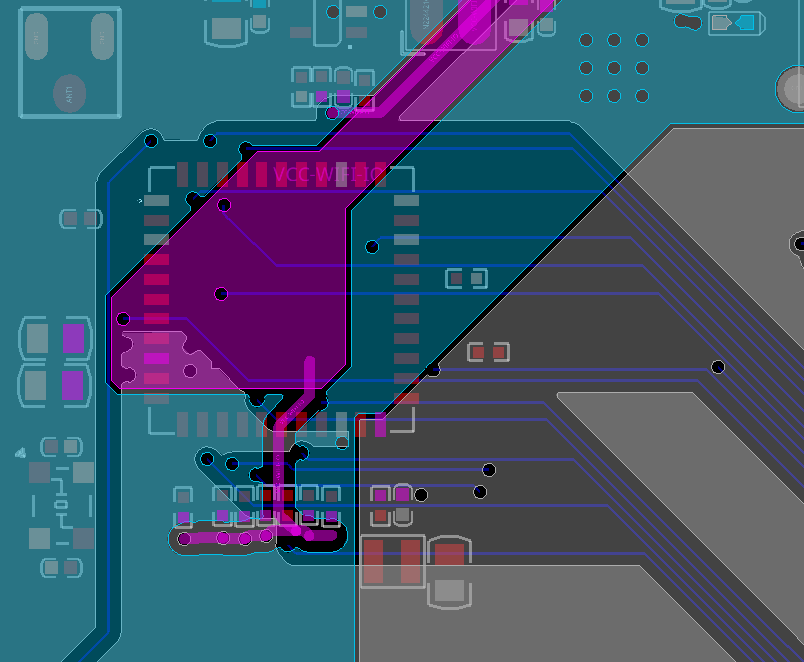

最大的问题是在wifi-sdio上:

首先走线乱,其次就是数据线参考平面跨分割了,当时没注意到,缺乏经验。

板子布局:

板子大致布局我觉得没有问题,但是整个板子的线都很凌乱,没有横七竖八的美观,所以布局还需很大改进。

然后就是打板,嘉立创jlc2313结构打板有点慢,板子到手总共用了10天。

然后就是焊焊焊,目前还没焊完,只有周末有时间,平时加班也比较多,焊得也比较丑,哈哈哈哈

由于我自己不懂linux,所以也使用的是友善之壁的固件,醋酸胶布下面是一个散热片,真的比较烫:

使用debian

先写到这,自己先慢慢学习linux,希望能学会,希望大佬们也能多给我一些建议,特别是PCB Layout上的缺陷与不足,我好及时改进,也是非常难得的学习机会。

最后,后面可能会问到一些linux软件方面的问题,希望大佬们多多帮忙解答,爱你们,么么哒!!

附件(allegro 17.4):

H3.zip

离线

楼主 #8 2021-05-27 19:19:40 分享评论

- laplace

- 会员

- 注册时间: 2021-03-05

- 已发帖子: 18

- 积分: 65

Re: 全志H3四层板制作分享,从开始学allegro 到完成第一块高速板

厉害,666666

过奖了,哈哈哈

离线

楼主 #9 2021-05-27 19:20:18 分享评论

- laplace

- 会员

- 注册时间: 2021-03-05

- 已发帖子: 18

- 积分: 65

Re: 全志H3四层板制作分享,从开始学allegro 到完成第一块高速板

厉害,666666

过奖了,菜鸟一枚。嘻嘻嘻

离线

楼主 #15 2021-09-07 15:38:30 分享评论

- laplace

- 会员

- 注册时间: 2021-03-05

- 已发帖子: 18

- 积分: 65

Re: 全志H3四层板制作分享,从开始学allegro 到完成第一块高速板

还有,楼主是怎么焊接BGA的H3与DDR的呀?可以简单说一下步骤吗

我是使用的BGA返修台。

离线

楼主 #19 2021-12-30 17:26:58 分享评论

- laplace

- 会员

- 注册时间: 2021-03-05

- 已发帖子: 18

- 积分: 65

Re: 全志H3四层板制作分享,从开始学allegro 到完成第一块高速板

还有,楼主是怎么焊接BGA的H3与DDR的呀?可以简单说一下步骤吗

BGA H用的BGA焊台,DDR用的风枪

离线

楼主 #20 2021-12-30 17:28:01 分享评论

- laplace

- 会员

- 注册时间: 2021-03-05

- 已发帖子: 18

- 积分: 65

Re: 全志H3四层板制作分享,从开始学allegro 到完成第一块高速板

楼主固件怎么和你自己画的板子匹配的?

固件使用HDMI输出的 就有输出 也不是所有外设都工作了,没有声音

离线

楼主 #24 2022-01-04 10:03:24 分享评论

- laplace

- 会员

- 注册时间: 2021-03-05

- 已发帖子: 18

- 积分: 65

Re: 全志H3四层板制作分享,从开始学allegro 到完成第一块高速板

DDR布线是不是板上最复杂的了?需要注意哪些地方?

确实 ddr走出来了 其他就简单了 需要注意阻抗,间距,等长,组内过孔一致且不超过两个等 具体可以查看DDR3走线要求

离线

楼主 #40 2023-10-06 13:29:12 分享评论

- laplace

- 会员

- 注册时间: 2021-03-05

- 已发帖子: 18

- 积分: 65

Re: 全志H3四层板制作分享,从开始学allegro 到完成第一块高速板

楼主您好!请教一下,为啥主控到DDR1/DDR2地址线之间长度误差可以是600mil这么大?

这个是参考的全志硬件设计指南,全志给的建议。

离线